Tekmos Talks Newsletters

A newsletter for the semiconductor industry

Tekmos Talks 2017

|

|

||

| A Newsletter for the Semiconductor Industry | ||

| December 2017 | ||

| Reprogrammable IP for High Temperature ASICs | ||

|

Tekmos makes ASICs, which are definitely not programmable. But sometimes, customers need a little bit of programmability in an ASIC. Just look at the increase in FPGAs in modern SOC design. So, we decided to add reprogrammable IP to our high temperature ASIC product offering. But what type of programmable IP? The high temperature process we use has limits, and one of the main limits is density. So, we decided to start with something small like a PAL. PALs (Programmable Array Logic) have been around for years. They were one of the first programmable devices, and lead the way into the development of FPGAs. We have one other issue with our technology, and that is it does not support non-volatile memories. Stored charge memories leak away at high temperature. So, we decided to make a RAM based PAL. We chose to make a 22V10 equivalent PAL. Starting with PALs has several advantages. First, the schematic is known, which simplifies the reverse engineering. Most of the work involves replacing the fuse array with a RAM. One interesting engineering point was the design of the wired-AND gate that the fuses are attached to. Most PALS used a pull-up resistor, and allowed the inputs to pull it low. This has the simplest layout, but continuously draws high current. And we were concerned that the increased leakages experienced at high temperature would cause this architecture to fail. So, we instead opted to build a discrete, 44-input AND gate. The layout is more complicated, but it has superior performance. Another advantage of copying existing PALs is that the programming instructions are a JEDEC standard. If we maintain fuse compatibility, there are a number of existing software programs that can be used to develop circuits. And most of these programs are available at no cost. In some cases, the source code is also available. Interfacing IP to the rest of the design is always an important issue. Our IP is designed to appear as a RAM to the rest of the ASIC. So, the interface becomes just a DMA into that RAM. We can set the data bus width to 8, 16, or 32 bits in size. Internally, the RAM is organized as 133 words of 44 bits. Call us and find out how you can add reprogrammability to your next high temperature ASIC. To learn more contact: Sales. |

||

| From the Desk of the President, Lynn Reed | ||

High Temperature ROM Design-Sense Amps In the previous two articles, we discussed ROM bits and word drivers. In this article, we will discuss the sense amps. Or more accurately, we will discuss the bit line precharge, the multiplexor, the sense amps, and the output latch. In the ROM, the bits can only pull to zero. To ever get to a logic one, we use a precharge circuit. That is a fancy name for a P-channel transistor. In between read cycles, the bit lines are kept precharged. When a read occurs, the precharge lines are turned off, and then a single word line is turned on. Depending on whether that bit has been programmed, the bit line will either remain at a one, or be pulled down to a zero. After the end of the cycle, the bit lines are precharged back to the one level. The size of the precharge transistor is not that critical. It must be large enough to precharge the bit line before the next cycle occurs. Generally, this can be accomplished in 3 or 4 nanoseconds. The most difficult thing about the precharge is the layout. Since there is one for every bit line it must fit within the width of a bit. In our case, the bit was so narrow that we could not make the precharge fit. As a result, we staggered the precharge transistors, taking up twice the height so that we could maintain the required width. After the precharge is an 8:1 mux. This consolidates 8 bit lines down to a single signal that will feed the sense amp. The mux is built out of N-channel transistors. They are arranged as 2:1 muxes in 3 stages, going from 8 to 4 to 2 to 1 signal. There is a slight complication in that each individual mux stage also requires a precharge. So, in addition to the 8-bit line precharges, we have to add 7 mux precharges. The mux is controlled by address lines A3, A4, and A5. The sense amp is quite different in a ROM than in a RAM. In a RAM, there are complimentary bit lines available, and the sense amp makes a differential measurement. Differential measurements are quite easy to make in MOS technologies. However, in the ROM, there is only a single bit line available. One might create a voltage reference, but there are difficulties in making a valid reference, and the margin available is only half that of a true differential signal. Instead of a voltage reference, we use time as a reference. We add one additional bit line to the ROM that is always programmed as a zero. This extra bit line closely tracks the performance of the rest of the ROM. So, when it reaches a zero level, we know that sufficient time has passed for any other bit line that is switching to a zero to reach a zero level. This turns the sense amp into a simple inverter. This inverter then feeds a latch. We make the latch transparent at the beginning of the cycle, and close it when the reference bit line reaches a zero. Starting from 568 bit lines, the muxes narrow it down to 71 bits, and those are stored in latches. The number 71 comes from 64 data bits and 7 error correcting bits. In our next article, we will cover how the ECC circuitry works, and how we wind up with a final data bus of 8, 16, or 32 bits in size. Contact us today at Sales for more information. |

||

| Inside Tekmos | ||

Tekmos Thanksgiving Celebration Every year, on the Friday before Thanksgiving, we have a company spread. The company covers the Turkey, and everyone else brings something. Since everyone makes their best dish, we have a very good meal. Jon Gehm experimented with a cherry pie, covered with whipped cream containing Madagascar vanilla. He was disappointed with the results, but no one else was, and there was none left over. Rick Holman had some excellent creamed corn with real cream. And of course, there was a lot of turkey, dressing, and gravy. There were some leftovers, but those were taken home by our younger employees, who are still hungry from their college days. |

||

| Technology Innovation | ||

|

Tekmos Product Technical Notes

November was a busy month for us. We received first silicon of a revision to our TK89C668 microcontroller. This was an analog adjustment to a pull-up current that was not centered on specification. We characterized the part, and found the adjusted current was an exact match to the design goals. This is proof that Spice simulations work. A few months ago, we invested in a probe test for our highest volume part. The first production material that we probed arrived at final test this month. This allows us to separate the fabrication yield from the assembly yield. We were surprised by how good a job our assembler is doing, as we now have almost no failures at final test. We also taped out on our new replacement for the 80C51RA2, 87C51RA2, 87C51RB2, 87C51RC2 and 87CRD2 microcontrollers. With 3 different package styles, that will provide us with 15 prototype lots to evaluate. It now looks like they will arrive back at Tekmos a few days before Christmas. We will have something to do should we tire of opening presents. |

||

| Thank You for Reading Tekmos Talks | ||

|

Thank you for reading Tekmos Talks and helping us celebrate 20 plus years. Sincerely, Lynn Reed, President

|

||

|

|

||

| A Newsletter for the Semiconductor Industry | ||

| November 2017 | ||

|

Tekmos offers solutions for product developers needing custom analog/mixed signal integration. Tekmos provides a fast and low cost solution to integrate many analog/mixed signal functions and intellectual property into a single device for very low NRE and low volume commitments to start production. We can convert your ideas, specifications, block diagrams into a device and build to order. Tekmos provides an all USA design center for development and testing. If required, we can use an all USA production flow for ITAR and export controlled products. Our capabilities are very attractive for Medical, Consumer, Defense and other low power products where custom integration is necessary to meet the products requirements. Major benefits include very low NRE to develop the device, fast turnaround of development and prototypes, and low volume commitments for starting production. Additional benefits are reduced engineering staff by customer to support custom projects with Tekmos, guaranteed results of a working chip in your product, and built-in design security to make your product very difficult to copy by competitors. Contact Sales for a quotation. |

||

| From the Desk of the President, Lynn Reed | ||

Replacing Obsolete Flash Memories Flash memories have been around long enough so that the original parts have gone obsolete. And while larger flashes could be used to replace older flashes, there are frequently differences in operating voltages, packaging, and programming algorithms which make this impractical. Tekmos has gotten around these issues by designing an ASIC to serve as an interface between the outside system and the newer flash. Tekmos then combines the flash and our ASIC in a single package using stacked die assembly techniques. This produces as drop-in replacement for the original part that can be manufactured in any quantity. Voltage CompatibilityMany older flash memories ran off of 5 volts. As the technology advanced, they switched to a 3 volt supply, but had 5 volt interfaces. Once the technology passed 130 nm, the parts became 3 volt only. To replace these parts, the Tekmos ASIC provides level translators and an internal voltage regulator. The level translators provide the 5 volt to 3 volt translation on the address and control lines, and a bidirectional translation for the data bus. Level translators work well, but they require time to work. This time is on the order of 8 ns, and since we need to have translators on both the address and data lines, this will add about 16 ns to the Flash access time. And that sets a lower bound on how fast of a Flash we can replace. Using 55 ns flash, we produce a part that can be no faster than about 75 ns. This number will increase if we have to include additional circuitry to mimic other flash functions. The ASIC also has to provide a 3.3 volt power supply for the flash. Flash memories have unusual power supply requirements. When they are being programmed, the supply current increases from idle to maximum in a few nanoseconds. This can be faster than a traditional voltage regulator can respond to. If that is the case, the power supply can droop, which could cause the flash to abort its write cycle, and then reduce the current draw. We address this by having a very high response speed voltage regulator which we designed. The price we pay for a quick response regulator is a limited input voltage range. Fortunately, most flash memories have a 10% tolerance on the input supply, which is well within the range of our regulator. Programming Algorithm CompatibilityThere are two main algorithms used to program Flash memories. These are the Intel / Micron algorithm and the Spansion / Fujitsu algorithm. In addition, really old Flash memories did not have an unlock algorithm. Instead, they used the presence of a programming voltage to initiate programming. The best solution is to use a modern flash that has the same programming algorithm. We can tie off the upper address lines, and have a good match. For the older chips, such as the 28F010, there are no existing Flash memories with the same programming algorithm. In those cases, we have to detect the programming cycle, and generate our own program sequence. The downside of this is that the additional circuitry in the address and data paths adds another 5 to 10 ns to the access time. Fortunately, many of the older Flash memories were slower, and so we have the margin. One possible problem with this approach is that if the programmer removes the voltage from our part at the end of the programming cycle, and our internal circuitry has not finished writing or erasing the past, then the write / erase operation can fail. Sector CompatibilityIt is desirable that the sector architecture of the new part match, or at least be compatible with the sectors used in the old part. We may be able to use address mapping to match the sector sizes. For example, a 64 KB sector could be used to replace a 32 KB sector. Typically, the newer Flash memories are larger, and that allows us flexibility in mapping the sectors. Note that the presence of sector mapping circuitry will add another 5 ns to the access time. High Voltage InputsThe really older flashes used the presence of a programming voltage (typically about 12 volts) to trigger a write / erase cycle. They also used this high voltage on pin A9 to read the manufacturer's ID. This high voltage poses a problem for our ASICs, which can be damaged by voltages in excess of 5.5 volts. Our solution is to use a series resistor to limit the voltage on the chip, and then use a lateral PNP transistor to detect the presence of the programming voltage. Special FeaturesIn some cases we must have our chip provide the original manufactures codes for part number and ID in order to maintain software compatibility. This can be done by intercepting the request, and taking over the data bus. Then we can provide whatever information is required. Tekmos Flash ProductsTekmos makes 5 flash replacements. These are the TK17LV040 FPGA serial programming memory, and the TK28F256, TK28F512, TK28F010, and TK28F020 parallel flashes. We have other sizes under development. Contact us today at Sales for more information. |

||

| Inside Tekmos | ||

|

Movie Night We have been trying out a new activity during October. On Thursday nights, we are showing an old movie, and providing pizza. This started with the realization that there are many movies that our younger employees have never seen, and that our older employees have forgotten. So we are remedying that by showing movies from the 40s to the 60s that have had significant cultural influence. We started with the early James Bond movies, and we will follow it up with some Bogart movies. After that, the spaghetti westerns, and then we will pick others. Our plan is to pick a theme, and then watch 3 or 4 of the better movies from that theme. And there are enough movies from that time frame to keep us occupied for years. |

||

| Technology Innovation | ||

|

Space, the Final Frontier Brings the Tricorder to Healthcare

Healthcare accounts for almost 1/5th of the US GDP, meaning we need to start making serious investments to improvements that make healthcare more affordable and efficient. Qualcomm has a contest, called XPrize, that was extended in 2017 for 7 final teams developing the Tricorder featured in the Star Trek series. The winner receives $10 million to bring the device to reality. In April the winner was awarded. In the fictional Star Trek universe, a tricorder is a multifunction hand-held device used for sensor scanning, data analysis and recording data. The medical tricorder is used by doctors to help diagnose diseases and collect bodily information about a patient. XPRIZE, the global leader in incentivized prize competitions, and the Qualcomm Foundation have awarded millions of dollars to the finalist teams of the Qualcomm Tricorder XPRIZE, including a top prize of $2.6 million to the Pennsylvania-based team, Final Frontier Medical Devices, led by brothers Dr. Basil Harris, an emergency medicine physician, and George Harris, a network engineer. Final Frontier developed an affordable device that can diagnose and interpret a defined set of 13 health conditions to various degrees, while continuously monitoring five vital health metrics. After four years of development, team Final Frontier created DxtER (pronounced "Dexter"), an artificial intelligence-based engine that learns to diagnose medical conditions by integrating learnings from clinical emergency medicine with data analysis from actual patients. DxtER includes a group of non-invasive sensors that are designed to collect data about vital signs, body chemistry and biological functions. This information is then synthesized in the device's diagnostic engine to make a quick and accurate assessment. Qualcomm and the Roddenberry Foundation have contributed additional funding to the continued pursuit and development of DxtER. "I'm a doctor, not a brick layer, Jim." |

||

| Thank You for Reading Tekmos Talks | ||

|

Thank you for reading Tekmos Talks and helping us celebrate 20 plus years. Sincerely, Lynn Reed, President

|

||

|

|

||

| A Newsletter for the Semiconductor Industry | ||

| October 2017 | ||

|

Tekmos provides fast integration for small wearable, battery powered products... Tekmos provides a fast and low cost solution to integrate customer designs into a small form factor package using its unique low cost die stacking capabilities. There is significant time to market advantages merging various chips into a vertical stack to optimize integration and eliminate large NREs and high risk. The Tekmos Unify solution includes a design and manufacturing service to handle all engineering from design through production shipment of final tested products. This service is ideal for companies wishing to integrate their standard ICs to permit more room for other features or special batteries to expand features and extend the operating life of their products. Contact Sales for a quotation. |

||

| From the Desk of the President, Lynn Reed | ||

Word Line Drivers In my last article, I discussed the design of the ROM bits. This article will cover the word line drivers. Our ROM has 512 word lines. A brute force approach would use a 10-input AND gate to decode each word line, nine inputs for the address lines, and the tenth input to disable all word lines during precharge. But 10-input AND gates are both large and slow, so a better way must be used. We use a 2-to-4 demuxer for eight of the address lines. The ninth address line is gated with the precharge. This allows a 5-input AND gate to be used instead of the 10-input gate. But this solution also has problems. In a NOR ROM, the word line drivers must be the same height as the ROM bit. And that is not enough room to put in a AND gate. The next solution is to create a double height word driver that can decode both words. The schematic changes to a 4 input NOR gate that drives a pair of 2-input NAND gates, each driving a word line through inverters. This is a tight fit, but can be made to work by mirroring each dual word line driver so that they can share common supplies. Three of the four inputs of the NOR gate are common between the two mirrored drivers, and that saves more room. The NOR and NAND gates are minimum sized devices, while the word line has 569 loads. In order to drive large loads, it is necessary to use a chain of inverters, each one being stronger than the preceding one. The optimum ratio between inverters is "e". But using "e" as the ratio results in a very large inverter driving the word line. And that means 512 large inverters for all the word lines. We resolve this by letting the final ratio be a larger number. There is a tradeoff between reducing the inverter size, which increases the ROM access time, but reduces the area and reduces the peak current draws. After multiple spice runs, we set the output inverter ratio to be about 95:1. This also allows the inverter chain to be three inverters long. One thing that worked in our favor is that the bit cells start to conduct as soon as the word lines exceed the N-channel threshold, which is close to the starting voltage. The address lines A6:A14 control the word decode. We have the option of latching them during the ROM read cycle, or not. If we choose to latch them, then we can either include the latches in the ROM core, or latch them externally. It is not required to latch the addresses, but it is safer to do so. Our final decision will be determined by the physical layout. If there is room for the latches, then we will add them. If not, we will leave that as an option for the chip level designer that uses this ROM core. In the next column, I will cover the bit line muxes, the sense amps, and the ECC logic. Contact us today at Sales for more information. |

||

| Cyber Security | ||

|

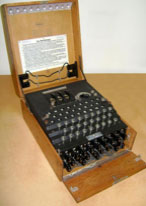

Cyber Security & the Enigma Machine

The Enigma machine was quite clever, especially considering it was created back in the 1930s. Not only was there a large number of codes, the algorithm changed with each character. And the Germans used different codes for the Army, Navy, and Air Force, and different codes for different hierarchies within the armed services. The lecture covered the machine's schematic, and how it worked internally. It was an electrical mechanical machine, and used three disks that electrically connected pairs of letters. The disks rotated with each key stroke, producing a different code for each character. Because the ultimate effect was to create a pair of letters that were swapped, the same machine could be used to encode or decode a message. How the code was broken daily was equally interesting. Had the Germans followed their own rules, the code would have been almost unbreakable. But the Germans were sloppy with their procedures, and that made breaking the code easier. As an example, there was a German outpost that sent the same status report daily when nothing was happening. Allied forces were instructed to leave this outpost alone, and not even overfly it. With nothing to report, sending the same message made it easier to decrypt the daily code. Another exploited weakness was that the Germans to end messages with "Heil Hitler". Knowing the last 10 characters was a great assist in cracking the code. These and other human errors had the effect of reducing billions of combinations down to more reasonable numbers, that could then be cracked through a trial and error procedure. And those lessons are still applicable today. |

||

| Inside Tekmos | ||

|

Summer Intern, Clayton Abel

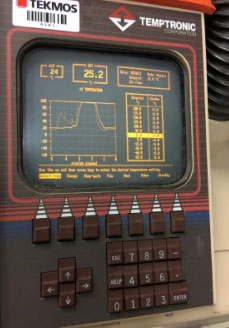

The main electrical specification for flash memories is the access time. It seems like a simple task, but it isn't. The actual access time varies slightly from pin to pin. It also depends on the previous data read from the part. And like all other measurements, it is a function of temperature, voltage, and output loading. Our production testers measure access time. But there are delays to and from the pin electronics, and the tester capacitance is too high for the specified measurement. The data sheets also use a diode - resistor biased load to improve timing performance. Our task is to measure our parts under specified conditions, and use that information to set the tester parameters accordingly. It was Clay's job to make the measurements. We rented a high-performance scope for the measurements. But could we trust it? So, Clay's first task was to measure the speed of light by looking at the propagation time of a signal down a 10-foot wire. It was in agreement with previous measurements. Had it not been, Clay could have gotten a Nobel prize in addition to a paycheck. With the calibration out of the way, Clay spent the rest of his time making hundreds of measurements on multiple parts from multiple lots over the temperature and voltage extremes. Then he helped write the report that constitutes our product validation. Clay did excellent work for us, and my only regret is that he will graduate in May, and no longer be available for summer work. |

||

| Thank You for Reading Tekmos Talks | ||

|

Thank you for reading Tekmos Talks and helping us celebrate 20 plus years. Sincerely, Lynn Reed, President

|

||

|

|

||||||||||||||||||||||||

| A Newsletter for the Semiconductor Industry | ||||||||||||||||||||||||

| September 2017 | ||||||||||||||||||||||||

|

Welcome to Tekmos Talks September 2017. In this issue we are going to talk about ROM Design, Inside Tekmos and the solar eclipse, feature a product, and talk about drone technology. We extend our best wishes to our neighbors along the Gulf Coast. If you would like to help people affected by Harvey please click on the Rebuild Texas image above. |

||||||||||||||||||||||||

| From the Desk of the President, Lynn Reed | ||||||||||||||||||||||||

The Design of a Masked ROM This is the first in a series of articles covering the design of a masked ROM. It will cover the choices behind making a masked ROM, and the design of the ROM array. The first question that should be asked is why would anyone ever design a masked ROM when you have flash? It is a good question, and we have two answers. The first is that this ROM is being designed for high temperature applications, and flash memories lose their data at high temperature. Flash memories use stored charge, which will leak away over time. The leakage rate is a function of temperature, and roughly doubles with every 10ºC rise in temperature. A 10-year life at 125ºC reduces to a matter of hours at 275ºC. And that is if the flash is built on a fully depleted SOI CMOS process, which most are not. This reduction in flash lifetime can be partially addressed by frequent refresh operations. A second reason for considering a masked ROM is that many processes do not support the flash technology, whereas all processes can be used to make a masked ROM. Once the decision has been made to make a masked ROM, the next choice is the architecture of the ROM array. There are two options: NAND and NOR. NAND has better density, but is slower, and uses more power. NOR has worst density, but is faster and uses less power. In the past, all our ROMs have used the NAND architecture. This time, we opted to use the NOR architecture. At high temperature, everything runs slower. In computer systems, the memory speed is usually the bottleneck, and so it makes sense to design the ROM for maximum speed. Our initial design goal is to have a sub 100 ns access time at 300ºC. The design of the ROM array is about as simple as possible. Each ROM bit consists of a single N-channel transistor. The source is tied to ground, the gate is connected to the word line, and the drain is connected to the bit lines through the programmable contact. If there is a contact, the bit line goes to zero. If there is no contact, the bit line stays as a one. The poly word line resembles a transmission line, and it can take the signal a long time to go from one end to the other. We are using a special high temperature process that does not support salicide. As a result, the poly is quite resistive. We address that by running a metal line over the poly, and connect it to the poly every 8 bits. This greatly improves the ROM speed for those bits located the furthest away from the word line drivers. The next thing that we should worry about is the impedance of the ground lines. This is aggravated by the use of Tungsten as an interconnect metal. We have to use Tungsten because Aluminum has metal migration problems at elevated temperatures. In order to lower the ground impedance, we run perpendicular ground lines every 64 bit lines that convert the ground line from a single stripe into a grid. This allows every ground line in the array to help lower the impedance. We do have to add additional bits. The initial ROM was an array of 512 rows by 512 columns, for a total of 256K bits. We will group every 8 bit lines together to produce a single output bit. This produces a 64 bit word. To improve reliability, we are adding ECC to the ROM, which will require 7 more output bits, or 56 more bit lines. And we need to add one additional bit line which is always programmed to provide a reference for the self-timing. This will be discussed later. At this point, I have an array with 512 rows and 569 columns. I will discuss the word lines and their decodes in the next article. Contact us today at Sales for more information. |

||||||||||||||||||||||||

| Inside Tekmos, Lynn Reed | ||||||||||||||||||||||||

|

Tekmos & Solar Eclipse Totality, August 21st 2017

None of us had any experience with RVs, but we learned fast. Now I know how burning propane can keep a refrigerator cool, and how to deal with water pumps, generators, and the dreaded black water.

The house where we were camped had chickens, goats, and a couple of calves. The son of the owner took us for a trip around the place, and showed us everything, including a box of newborn kittens in the barn. I also learned that there are chickens that laid red, green, and blue eggs. I even had green eggs and ham for my Monday breakfast. This totally surprised me in that I always thought green eggs were a fairy tale from Dr. Seuss. How many other of my cherished beliefs are also wrong?

Then it was over and time to start the 18-hour drive back to Texas. |

||||||||||||||||||||||||

| Product Feature | ||||||||||||||||||||||||

|

68HC705 Microcontrollers Tekmos has a 68HC705 design that can be used to replace many variations of the 68HC05 and 68705 microcontrollers. Our first part is the TK68HC05B6 with 6K of ROM. Our second part is the user programmable TK68HC705C8A / TK68HC705C9A devices. These parts use flash memory as contrasted to the original part's One Time Programmable (OTP) EPROM. The 68HC705B16N and 68HC705B32 are available with a longer lead time. The Tekmos 68HC05 has been carefully designed to duplicate the original 68HC05 on a clock for clock basis. This guarantees complete compatibility with existing code. Even timing loops will work perfectly. Tekmos is currently seeking customers willing to evaluate our daughtercard-based breadboard in their system for the purposes of design verification. Below is a list of 68HC705 microcontroller variants that are either available immediately or under development. If you need a version not listed here or have any questions please: Contact Us.

|

||||||||||||||||||||||||

| Drone Technology | ||||||||||||||||||||||||

|

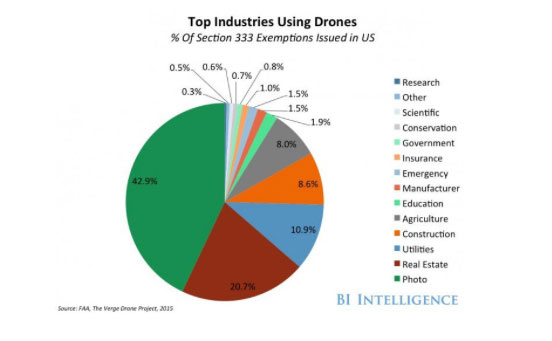

Drone Technology & Uses Drones are the new technology to cell phones of the 90's with drones for amusement such as the earlier airplane models, drones for farming use, aerial photography, law enforcement, spying, military, search and rescue, and possible delivery of special product orders. Business Insider says of drones four sector major area of use: Military, Commercial, Personal, and Future Technology, "Increasing work efficiency and productivity, decreasing workload and production costs, improving accuracy, refining service and customer relations, and resolving security issues on a vast scale are a few of the top uses drones offer industries globally." Goldman Sachs predicts military spending will remain the main driver of drone spending in the coming years. They estimate that global militaries will spend $70 billion on drones by 2020. A single US Predator drone costs approximately $4 million, and total spending for the program is estimated at a total of almost $2.4 billion. The impact of commercial drones could be $82 billion and a 100,000 job boost to the U.S. economy by 2025, per AUVSI. According to airdronecraze, an Amazon Services LLC affiliate advertising program website, drone technology has seven potential generations, and most current technology sits in the fifth and sixth generations. Here is the breakdown of the technology generations:

|

||||||||||||||||||||||||

| Thank You for Reading Tekmos Talks | ||||||||||||||||||||||||

|

Thank you for reading Tekmos Talks and helping us celebrate 20 plus years. Sincerely, Lynn Reed, President

|

||||||||||||||||||||||||

|

|

||

| A Newsletter for the Semiconductor Industry | ||

| August 2017 | ||

|

Welcome to Tekmos Talks August 2017. In this issue of Tekmos Talks, we are going to talk about Complying with new NIST Standards,Medical Device Interoperability, a pictorial story of a recent visit to Queen's College in Cambridge, and feature a mixed signal high temperature product. Be sure to check out Tekmos technical services: Design and Verification, Test and Characterization, and Burn-in and Reliability. |

||

| From the Desk of the President, Lynn Reed | ||

Complying With New NIST Standards The National Institute for Standards and Technology recently released a set of standards for cyber security. Defense contractors are required to implement these standards by the end of 2017, and that applies to Tekmos. We started off already being compliant with about half of the standards. Achieving compliance with the other half of the standards is more of a challenge. One major area we are working on is formal documentation. The NIST standards require formal procedures for all aspects of cybersecurity. We already have informal procedures, but converting all of them to formal procedures is a major undertaking. The one advantage to creating all of this documentation is that it fits in with our AS9100 documentation we are creating for our certification audit later on this year. The second area of work is the addition of card readers to each PC to only allow authorized users on each work station. At first, this seems straightforward, but becomes more complicated when our testers are taken into account. The testers are tightly coupled to engineering, and so are part of our network. But they also run independently, and we have one operator taking care of multiple tester / handler configurations. It is not clear how we will address this. Another interesting area is the requirement of a whitelist for approved programs. Engineering will frequently try out new programs as part of their jobs. And so the procedures need to be written to allow this, while still providing security. There is still a lot to do, but we are optimistic that we will be compliant by the deadline. And give the increased cyber threats these days, it is good to be improving our defenses. Contact us today at Sales for more information. |

||

| Inside Tekmos | ||

|

HiTEN 2017 Tekmos returned to the United Kingdom as a sponsor for the International Conference and Exhibition on High Temperature Electronics Network (HiTEN 2017 ) Queen's College, Cambridge July 10-12. The event had a lower attendance in previous years, yet future opportunities were made networking, and evening walks to learn more about Cambridge. We stayed in the dorm rooms to get more of a feel of Queens' College, a constituent college of the University of Cambridge, England and one of the oldest and largest colleges of the university, founded in 1448 by Margaret of Anjou (the queen of Henry VI, who founded King's College). {igallery id=2179|cid=8|pid=2|type=category|children=0|addlinks=0|tags=|limit=0} |

||

| Product Feature | ||

|

High Temperature Mixed Signals High temperature electronics operate in one of the most demanding electronic environments. Junction leakage doubles with every 10ºC increase in temperature. For bulk silicon devices, the leakage becomes significant above 175ºC, and intolerable above 225ºC. And while digital logic can withstand some leakage, most analog circuits cannot. Leakage is a problem that cannot be overcome with clever design tricks. It requires a different process. And that process is SOI (Silicon On Insulator). In this process, oxygen is implanted beneath the devices. And the field oxide extends down to the implanted oxide layer, providing external isolation. Then, the diffusions are deep enough so that they too touch the buried oxide. This eliminates the bottom and sidewall junctions. And without a junction, there can be no junction leakage. There is a small junction between the source / drain diffusions and the transistor channel. So while the junctions have not been totally eliminated, they have been reduced in area by a factor of 1,000. And that gives the SOI process an additional 100ºC of operation. As with all engineering choices, there are tradeoffs. On the positive side, stray capacitance has been eliminated, along with the voltage dependency of diffused resistors. And with most wells tied to the transistor sources, the body effect has been eliminated. On the negative side, layout density is decreased, and overall layout is more difficult. There are no vertical bipolar devices, just lateral ones. We do not have an EEPROM cell, so trimming becomes more complicated. And the 1u technology limits the circuit size. Applications To start with, anything that can be done in bulk silicon can also be done in the SOI process. In the down-hole environment, there is demand for instrumentation amps, ADCs, DACs, and the occasional op-amp. All of these are easily made, and because of the lack of junctions, will have better performance than achieved with bulk devices. Many down-hole measurements are made on low frequency signals, allowing Sigma-Delta ADCs to be used with up to 24-bit accuracy. And since the SOI devices are totally isolated from the substrate, the analog supplies can be +/- 2.5v volts, and still work with a digital section operating from a 5 volt supply. For more information on High Temperature Mixed Signals... |

||

| Medical Device Interoperability & FDA Standards | ||

|

Medical Device Interoperability & FDA Standards As the advancement of medical care and medical electronic devices continues to evolve, the FDA has created a set of standards to manage medical device interoperability. Medical device interoperability is: the ability to safely, securely, and effectively exchange and use information among one or more devices, products, technologies, or systems. This exchanged information can be used in a variety of ways including display, store, interpret, analyze, and automatically act on or control another product. Beginning in 2010 the FDA has brought together various stakeholders to promote collaboration, identify challenges and promote standardization for medical device interoperability. The FDA released a draft guidance, Design Considerations and Pre-market Submission Recommendations for Interoperable Medical Devices. "The focus of this draft guidance is to help manufacturers design and develop safe, effective, and interoperable medical devices by outlining important design considerations and providing clarity on the agency's recommendations for submitting interoperability-related information in premarket submissions and labeling."(FDA) In 2013, the FDA officially recognized an initial set of standards manufacturers could use to improve patient care by making sure devices work well together. The FDA continues to recognize consensus standards, such as ASTM F2761-09 (2013): Medical Devices And Medical Systems - Essential Safety Requirements For Equipment Comprising The Patient-Centric Integrated Clinical Environment, that are relevant to the development and design of interoperable medical devices and encourages their use. Contact Sales@Tekmos.com if you would like to discuss Medical Device Interoperability & FDA Standards. |

||

| Thank You for Reading Tekmos Talks | ||

|

Thank you for reading Tekmos Talks and helping us celebrate 20 plus years. Sincerely, Lynn Reed, President

|

||

|

|

||||||||||||

| A Newsletter for the Semiconductor Industry | ||||||||||||

| July 2017 | ||||||||||||

|

Welcome to Tekmos Talks July 2017. In this issue of Tekmos Talks, we are going to talk about RISC-V, our upcoming visit to the International Conference and Exhibition on High Temperature Electronics Network (HiTEN 2017) Queen's College, our recent trip to Space Expo 2017, and feature a high temperature chip product. Be sure to check out Tekmos technical services: Design and Verification, Test and Characterization, and Burn-in and Reliability. |

||||||||||||

| From the Desk of the President | ||||||||||||

|

RISC-V R & D

Tekmos serves several high reliability markets, such as aerospace, military, and oil. It is therefore only natural that much of our internal R&D efforts are directed toward increasing the reliability of our products. One of these efforts is aimed at improving the reliability of processors. One way to do so is using a triple redundancy for all flops in the processor, a technique called RHBD (Rad-Hard By Design). This works, but is a brute force approach that at a minimum, triples the circuit size. We have another approach that may only add a 30% overhead. To verify this approach, we need a processor to try it out on. There are many processors out in the market, but they come with licensing fees and restrictions on changes to the internal architecture. And we need to modify the internal architectures. So, we chose the RISC V processor, which is an open source processor from Berkley. An interesting aspect of this processor is that it is defined by the instruction set, rather than the hardware. The RISC V processor is finding increasing acceptance, and is supported by several development tools. Our first step was to get the basic design up and running in our simulator. Then came the more difficult task to fully understand the design. This is where we are now. Next, we use the RISC V as a test bed to prove out our reliability concepts. What is next beyond that is a little uncertain, and is more of a marketing decision. Check back with us in a year and see how it turns out. Contact us today at Sales for more information. |

||||||||||||

| Tekmos Upcoming Events | ||||||||||||

|

HiTEN 2017 Tekmos will be returning to the United Kingdom as a sponsor for the International Conference and Exhibition on High Temperature Electronics Network (HiTEN 2017 ) Queen's College, Cambridge July 10-12. Queens' College is a constituent college of the University of Cambridge, England and one of the oldest and largest colleges of the university, founded in 1448 by Margaret of Anjou (the queen of Henry VI, who founded King's College). One must not confuse it with Queen's College, Oxford founded in 1341. Visiting engineers to the conference should be intrigued by the Mathematical Bridge located on campus, officially known as the Wooden Footbridge. It was designed by William Etheridge a carpenter from a long line of such, and built by James Essex the Younger. The bridge is 50 feet 8 inches (15·44 metres) long. The angle between two adjacent radials (except the ones on the abutments) is one 32nd of a revolution. The arch is composed of tangents to a circle of radius 32 feet. The arrangement of timbers is a series of tangents that describe the arc of the bridge, with radial members to tie the tangents together and triangulate the structure, making it rigid and self-supporting. This type of structure, technically tangent and radial trussing, is an efficient structural use of timber, and was also used for the timber supporting arches (centering) used for building stone bridges. Analysis of the design shows that the tangent members are almost entirely under compression, while the radial timbers are almost entirely subject to tension with very little bending stress, or to put it another way, the tangent and radial elements elegantly express the forces involved in arched construction. |

||||||||||||

| Product Feature | ||||||||||||

|

TK89H51B The TK89H51B family is based on the 8051 architecture, is designed to work in high temperature environments up to 210ºC. There are three versions, defined by package size. The "A" version has full functionality while the lower pin count "B" and "C" versions containing a subset of the functions. The "A" version of the TK89H51B provides a non-multiplexed address and data bus, the 8-bit ADC, three additional parallel ports, and the SPI port. The "A" version also supports ISP, allowing for the downloading of programs into an existing system using HEX records. After the user program has been received, the processor jumps to location 0000 for further operation. The TK89H51B family is made on a 0.6u bulk silicon technology process which has a long and successful history. The TK80H51B family contains seven 8-bit bidirectional parallel ports, two external interrupt sources, three timer/counters, a serial port with a hardware interrupt capability and a frame error detect flag, power management, a programmable counter array (PCA), an 8-bit, 8-channel ADC, and a SPI port. These peripherals are supported by a multiple source, four level interrupt capability. The core processor contains 256 bytes of scratchpad RAM and another 256 bits of XRAM that can be used as program storage. We have been using a "H" designator for the 8051 series to indicate high temperature. But now that we have both bulk and SOI parts underway, we find it necessary to create new part numbers. In the past, other 8051 vendors have differentiated their parts with a suffix, and so we followed that procedure. Here is our numbering system for the 0.6u, high temperature 8051s:

Request for Product Information To request information click here TK89H51B |

||||||||||||

| Inside Tekmos Visit to Space Expo | ||||||||||||

|

Space Tech Expo 2017 Show Tekmos attended the Space Tech Expo 2017 in Pasadena in late May.

The conference examined questions and issues including:

Contact Sales@Tekmos.com if you would like to discuss radar or other applications for Contact devices. |

||||||||||||

| Thank You for Reading Tekmos Talks | ||||||||||||

|

Thank you for reading Tekmos Talks and helping us celebrate 20 plus years. Sincerely, Lynn Reed, President

|

||||||||||||

|

|

| A Newsletter for the Semiconductor Industry |

| June 2017 |

|

Welcome to Tekmos Talks June 2017 and 20 Years of Solutions. In this issue of Tekmos Talks, we are going to talk about some of the Services Tekmos offers. We are primarily a provider of ASICs and microprocessors, but the capabilities we use for these circuits are also available individually. Overall, our services can be broken down into the three areas of Design and Verification, Test and Characterization, and Burn-in and Reliability. |

| Design and Verification Services |

|

Design and Verification Services Sometimes, a project needs additional engineering resources. When that happens, Tekmos design engineers are available to help. Digital ASIC DesignWorking from your specifications, Tekmos can create digital designs and layouts in your preferred process technology. We can also assist with IP selection and interfacing. Mixed Signal ASIC DesignNot all designs are digital. Tekmos can design the analog portions, and provide the design in either schematic form or a GDS layout in the process technology of your choice. FPGA DesignOur designs are not just for ASICs. We can also develop FPGA based designs, in any of the FPGA families. Internally, it is our standard practice to implement our processors in an FPGA before we commit to silicon. This has given us a great deal of experience in working within the FPGA environment.

IP DesignSometimes a design needs an IP block. These are usually a specific peripheral to a processor, or a communications interface. IP locks serve as an efficient way of partitioning a design so that multiple designers can work on the same project. Many IP blocks can be purchased, while others need to be designed to meet a customer's specific requirements. Tekmos' designers can create IP to your specifications. The IP can be supported with simulations and design documentation. Design VerificationThe best way to insure a robust and working design is to divide the design effort into two teams. The design team creates the design, and the verification team writes simulations to check the work based on the original specifications. It is desirable for the verification team to be separate from the design team, to avoid their effort being influenced by the design team. This type of activity is detailed in such specifications as the FAA DO-254. Tekmos can serve as the independent design or verification team for your FPGA or ASIC. Product CharacterizationWhen a new part is released, the first question is does it work? To answer this question, it takes more than plugging it into a board and seeing if it powers up. To prove that it works, a sample needs to be functionally tested and have its AC and DC parameters measured over the temperature and voltage extremes. Tekmos offers a wide variety of services to support the customer's program requirements for device characterization. Contact us today at Sales for more information. |

| Test and Characterization Services |

|

Test and Characterization Services Tekmos offers test and characterization services. As a fabless semiconductor company, Tekmos has an internal test facility, with testers ranging up to 320 pins in size. We offer access to these facilities and the engineers that run them.

|

| Burn-In and Reliability |

|

Burn-In and Reliability Testing Tekmos also offers Burn-In and Reliability Testing services. The requirements can vary from part to part, and Tekmos can customize these services to meet your exact needs.

|

| Inside Tekmos Visit to Drone Show |

|

AUVSI Xponetial Drone Show We visited the AUVSI Xponential Drone Show to research prospective chip offerings. We are looking into offering radar processing chip sets, and it was a good opportunity to meet with sensor manufacturers and discuss their needs. It appears that there is a market opportunity for a radar chipset. But whether it is a correct choice for us will require further research.

Drones are an exciting area, and it was a real challenge to remain focused on our research. Because everywhere we looked, there were really interesting drones and applications. There were over 600 manufacturers exhibiting at the show. There were land, sea, and air drones. There were people selling applications using drones. And there were companies selling components to build drones. This included airframes, engines, propellers, hardware, sensors, and batteries. And for a person interested in drones, it was heaven. Contact Sales@Tekmos.com if you would like to discuss radar or other applications for Contact devices. |

| Thank You for Reading Tekmos Talks |

|

Thank you for reading Tekmos Talks and helping us celebrate 20 plus years. Sincerely, Lynn Reed, President

|

|

|

||

| A Newsletter for the Semiconductor Industry | ||

| May 2017 | ||

|

Welcome to Tekmos Talks May 2017 and 20 Years of Solutions. This month we will share about analog layout, a space parts conference, clock generators, "Inside Tekmos" camp out, and a featured product. |

||

| From the Desk of the President, Lynn Reed | ||

|

Analog Layout Approaches

Traditional analog layout uses what is called the full custom approach. Its advantage is that it generates the highest performance analog circuitry. The disadvantage is that it is very labor intensive, and takes a long time to complete. Analog circuitry frequently requires a second revision to adjust parameters. And with a full custom approach, that can mean extensive reworking of the layout, or even starting over. A second approach is to use pre-existing analog cells. Unfortunately, they may not be optimized for a particular application, and may have to be redone to meet the application requirements. Another approach is to use an analog array. The array consists of a mixture of transistors, resistors, and capacitors. The circuit is defined by the interconnect, which is typically done in metal or via fabric. Analog arrays generate acceptable performance with greatly reduced layout time and lower NRE charges. On the down side, the circuit is larger than a full custom part, and that adds to the volume production price. One of the main advantages of analog arrays is the savings in time. Not only is the layout time reduced, but frequently wafers can be started before the design is even finished. That is because the analog array contains sufficient flexibility to accommodate design changes to device sizes. Starting the arrays early can cut 4 to 5 weeks off of the wafer processing time. Also, the fab lot can be split, with some wafers held at the programming step, and that will allow a quick turn on the second revision as well. TransistorsSo what is an analog array? It begins with the need for analog transistors. While all transistors can be considered to be analog, it is frequently necessary in analog design for two adjacent transistors to have matching electrical characteristics. The better the matching, the better the analog performance. In the digital world, the only things that matter are speed and area, so very small transistors are used. But the smallest transistors will have the greatest mismatches, since naturally occurring edge variations are now a greater percentage of the transistor dimensions. These edge effects can be minimized by using larger transistors. The next decision is to determine what size transistors need to be included in the analog array. In general, there is a need for a number of identical width transistors that can be used as building blocks. There is also a need for a limited number of much wider transistors that can be used as the input stage of op-amps and comparators. And there is a need for longer L devices that can be used in low power applications. There is another need for digital devices that can be used to switch the capacitors used in filters and integrators. But even this is complicated. They can be drawn with equal P and N sizes to minimize switching noise, or they can be drawn with equal strengths for less distortion. Resistors and CapacitorsAn analog array also needs capacitors. In general, you can use a value made up from multiple unit capacitors. But you may also need a few capacitors that are odd sized, for use in scaling capacitor arrays that are used in analog to digital converter arrays. And we need resistors. Lots of unit resistors, with the unit being typically somewhere between 500 and 1000 ohms. The unit resistors can be combined in series and parallel to produce almost any desired value. There is also a need for larger value resistors. These might be well resistors, or specially implanted poly. Tiles for LayoutIt is convenient to group a select number of transistors, resistors, and capacitors, and group them together in a tile, and then use multiple instances of the tile to create the chip. Unfortunately, you will need more than one type of tile. For example, consider the needs of a band gap voltage reference. The bandgap design needs an array of bipolar transistors in order to work. Bandgaps are almost the only circuit element that needs this array of bipolar devices, and since you can generate multiple voltage references off of a single bandgap, you will likely only need one bandgap per chip. So it would be wasteful to include this bipolar array in every tile. There are several other cases where a specialized tile is a good idea. Even in a specialized tile, the other devices can be generic transistors that are programmed rather than being dedicated to a specific design. Reducing the Overall Cycle TimeWell before the design is done, the designer will have a very good idea of the amount of circuitry required to complete the design. This makes it possible to combine multiple tiles and digital logic to create a structured array very early in the design process. This array can be started in the fab, and receive the first 5 weeks of processing while the design of the personalization layers is being completed. This can remove an additional month from the overall design cycle, reducing the time to market for the final system. Give us a call, and learn how Tekmos can help you with your mixed signal applications. Contact us today at Sales for more information. Or fill out the FPGA questionnaire form here. Or to Request a Quote. |

||

| Space Parts Working Group | ||

|

Last month, Tekmos sent a representative to the annual meeting of the Space Parts Working Group. This is a meeting of government users of satellites, companies that make satellites, and component manufacturers that make parts for satellites. The meeting was for two days, and consisted of presentations from government users and the component manufacturers. It also presented a lot of networking opportunities. Tekmos sells several products into the aerospace market. We are also working on upgrading our quality system from ISO9001 up to AS9100, which is now being required by some of our customers. After that, the next step is changing our products to offer an even higher level of reliability. And the first stage of that process is to determine what are the limits with current parts. And that is why we were at the Space Parts Working Group. So, what did we learn? Being space related, radiation damage was a big topic. The higher the orbit, the greater the damage. As a subset of radiation, heavy ions are an increasing concern. Heavy ions are also a problem with the aviation market, and have been identified as a cause of commercial aviation engine failure in at least one instance. Another issue was bond wire integrity, as a result of corrosion, thermal cycle, and vibration during launch. And as with all semiconductor users, there were concerns about obsolescence and counterfeiting. These are all areas that will be addressed as we develop the next generation of Tekmos products. |

||

| Clock Generators | ||

|

Internal Oscillators Digital circuits (and some analog circuits as well) frequently need a clock. This is typically provided by either an external clock source, a crystal oscillator, an RC oscillator, or a ceramic resonator. These can be had to any desired level of accuracy. But they all require external components. When space is critical, a self-contained oscillator can be the solution. It is the smallest solution and the low-cost solution. The only problem is accuracy. A ring oscillator is easy to make, and is quite robust. But the accuracy is bad. The speed will vary with the square of the voltage, the -3/2 power of the temperature, and another +/- 20% with the wafer processing. This can result in 50% tolerances. And you will need around 1% tolerance to make a UART work. So how do you get there? Design is the answer. Limiting Voltage SensitivityWe cannot do anything about transistors being sensitive to voltage. But we can limit the voltage swing that the transistors see. So, the solution is to use a bandgap reference to generate a power supply for the ring oscillator. That takes care of one of the variables. Limiting Process SensitivityThe process sensitivity is primarily a result of normal variations in the thresholds of P and N transistors. We compensate for this with a trim. But what do we trim, and how do we do it? We have two options for trimming. The first involves adjusting the number of stages in a ring oscillator. This works best when there are a large number of stages. A better method is to adjust the ring oscillator supply voltage up or down to achieve the desired frequency. We use an op-amp to generate the supply voltage from the bandgap. The op-amp is biased with resistors that set the desired voltage. Letting the trim adjust the value of those resistors is an easy way to trim the frequency. At one time, lasers were used to cut resistors to trim them. That is still an option, but using NVM memory is a preferred solution. We put multiple resistors in the op-amp feedback network, and use transistors to select which resistors to use. The NVM then enables the transistors. Limiting Temperature SensitivityAs stated earlier, transistor strengths change as a function of the temperature to the -3/2 power. We can compensate for this temperature change by increasing the ring oscillator supply voltage when temperature increases. This part is challenging, and is beyond the scope of this article. But we would be happy to discuss it in greater detail should you need it in your application. |

||

| Product Feature Corner | ||

|

Product Feature:TK80C51FA Microcontroller The TK80C51FA combines most of the 8051 architecture peripherals into a single chip. It may be used as a pin-for-pin replacement for earlier generations of the 8051 such as the 80C31BH, the 80C32-1, the 80C32X2, and the 80C51FA. This design was created using the Tekmos configurable microprocessor technology, and implemented in our 0.35u CMOS process. The use of the original instruction timing insures that the original code will continue to perform correctly while running in the Tekmos design. The performance advantages resulting from the 0.35u process allow the Tekmos part to replace all of the earlier version's speed grades. The use of a current process also insures the long term availability of this part. For information about the TK80C51FA contact Sales. |

||

| Inside Tekmos | ||

|

Tekmos Spring Camp Out

Tekmos held our third camp out in April. We stayed at the Oxford Ranch, which was the same destination as the last two camp outs. The Oxford Ranch is a private campground that offers plenty of room and has decent toilet and shower facilities. The campground is about 70 miles away from Tekmos, and is located near the Enchanted Rock State Park. People have a choice between a day trip, or camping for 1 or 2 days. This time, everyone opted for a 2-day camp out. One new thing on the camp out was the appearance of a three-level tree house tent. From a "mature" point of view, it looks like it would cause serious back problems, but it does have room for plenty of visitors. As always, the groups split up on Saturday morning, with those under 30 going off to climb Enchanted Rock, and explore the cave at the top. Those over 30 remain in camp, and keep the coffee pot safe while we solve the world's problems. We have been improving our camping capabilities with each trip we make. Our main improvements for this trip were a camping coffee pot that works off a stove burner, and a better water supply. Next time we will work on a better kitchen organization and the addition of gourmet food to the menu. |

||

| Thank You for Reading Tekmos Talks | ||

|

Thank you for reading Tekmos Talks and helping us celebrate 20 plus years. Sincerely, Lynn Reed, President

|

||

|

|

||

| A Newsletter for the Semiconductor Industry | ||

| April 2017 | ||

|

Welcome to Tekmos Talks April 2017 and our 20th Year Anniversary Celebration. We want to extend our heartfelt gratitude to all of our customers, distributors, sales and staff for a great 20 years. We will share some stories of our success, talk about quality, and feature a product. |

||

| From the Desk of the President, Lynn Reed | ||

|

20 Years of Solutions

April marks the 20th anniversary of Tekmos' founding. Twenty years ago, James Betts and Lynn Reed left their jobs in California, moved to Austin, and started Tekmos. One of the more difficult things to do in a new company is to choose a name. We liked Tekmos, and when we googled it, there were no other hits, and we claimed it for ourselves. Starting as a design center, we made the transition into a fabless semiconductor supplier two years later. We started by making digital ASICs, branched into Mixed Signal ASICs, and from there into standard products such as microprocessors, specialty memories, and peripherals. We also expanded from our original telecom emphasis into industrial, military, medical, and high temperature oil markets. We just started work on our 830th chip. Looking back, it seems that our more interesting projects have all been related to either man-made or natural disasters. In 2005, hurricane Katrina devastated New Orleans. This included the loss of the neighborhood phone switches. These switches relied on a custom chip that had been made at VLSI Technology, which had been acquired by Phillips, and whose fab had since been shut down. There was intense pressure to make 60,000 new chips, which were necessary for the full restoration of phone service in New Orleans. We got the job, since it had a mixed signal component, and so other companies declined to bid. The chip was a complicated one, with a lot of dual port RAM, and an embedded phase locked loop. We undertook a rush program to re-implement the design, and get it fabricated. Everything was expedited. This included working over the Christmas holidays, and putting in some very long days. In one event that stands out, we completed testing the first prototypes at about 2 AM on a Sunday morning. The customer purchasing agent was with us, and he arranged for a UPS pickup at that time, and the part to be flown directly to Mexico for assembly later on that day. We were surprised that such a thing could even be done. We delivered, and phone service was restored. In 2011, the Tohoku earthquake occurred, which devastated the Japanese city of Sendai. Freescale had a fab in Sendai that was destroyed. The loss of that fab meant that they were unable to deliver what was to be a last time buy on microcontrollers to many customers. We set up an agreement with Freescale where we provided replacements for about 20 different microcontrollers. To do so, we designed a special gate array that contained ROM, EEPROM, and an ADC. This reduced our development time, and allowed us to switch devices part way through the manufacturing cycle if necessary in order to meet a particular demand. One of the more difficult challenges was to recreate the 68020 microprocessor. The yield of this part was very sensitive to variations in poly sheet resistance, and the Sendai fab was the only Freescale fab capable of holding the required poly tolerances. And to complicate things, the original design documents had been lost. The only documentation available was the GDS data base and the production test vectors. All 51 of them. The chip had been designed using a combination of NMOS dynamic logic and CMOS static logic. Our design approach was to use our layout verification tool to extract the spice netlist from the layout. We then post processed the netlist to extract individual gates, and then to combine gates into higher order functions such as flops. We converted all dynamic logic into static logic, and re-implemented complex gates into collections of simple gates. And some of the complex logic gates were quite complex. Many of them had over 100 inputs. Then we began an iterative process, converting the production test into Verilog test bench vectors, and using them to check the design. Errors were corrected, and the simulations rerun to find the next error. When all of the errors were fixed. We made silicon. We had many problems doing the 68020. The most difficult one was a case where the original design had transferred data onto a data bus, and left it there for a clock cycle. In essence, it was using the data bus as a dynamic 32-bit register. The circuit was not working, and we had a very hard time finding something that wasn't there. Once we realized what was going on, we had to add the register to make it work. Not all disasters are caused by nature. Some are caused by men. One of our customers approached us with an obsolete FPGA that needed replacing. However, the original design files had been misplaced, and because of layoffs, the original engineers we gone as well. All that the customer had was the bitstream. In order to replace the design, we had to reverse engineer the bitstream. We would not do this if it were a case of someone trying to copy another design. But we will do it for the original owner. This was not an easy task. After deciphering the bitstream, we created a Verilog model of the FPGA, and loaded it with the bitstream. Then we used Synopsys to reduce the FPGA model to gates, which we then placed and routed. This has been just a few of our stories. We have similar ones for each of the areas we operate in. Military stories, medical device stories, implantable stories, oil stories. Twenty years of stories. It has been fun and we look forward to the next twenty years. Contact us today at Sales for more information. Or fill out the FPGA questionnaire form here. Or to Request a Quote. |

||

| Quality Control, From the Desk of Director of Operations | ||

|

I Agree With Deming, By Jon Gehm As a young boy, I can still hear my grandfather patiently encouraging my efforts to improve my skill with an ax. He had an interest in that, as much of his pasture land was covered in small mesquite trees. He had cattle, and more grass land and less mesquite was a good thing in his mind. It also gave me a way to make money during the summer between school years. Unfortunately, my early system for cutting trees was random and frantic hacking all up and down the tree trunk. When I did manage to chop a small tree down, it was a minor miracle. "Yes sir, I sure do see a lot of activity. Now, if we can just work a little bit more on the achievement." Wait. Was that a compliment? Maybe not. My Paw Paw had a funny way of saying one thing, but when you thought about it, it sure sounded like he meant something else. I learned to listen for those bits of wisdom, from him as well as in the writings and words of others. Another person I found worth learning from is Dr. W. Edwards Deming. He lived from 1900 - 1993, and was considered by many to be the founder of the third wave of the industrial revolution. He was definitely a leading speaker for Quality on a global scale, and is still considered something of a folk hero in Japan. He could also make a point with very few words. Deming said that, "Every system is perfectly designed to get the result that it does." And that "a bad system will beat a good person every time." Well, that does sound a little bit like my early ax handling skills on those trees. Maybe Paw Paw was on to something. But Dr. Deming didn't stop there. He also said, "We should work on our process, not the outcome of our process." Further making the point that "managing by results is like looking in the rear view mirror." To my credit, I did adjust my approach to chopping mesquite trees. I found that a certain angle and specific placement of the blade resulted in a lot less work, with many more trees lying on the ground. I learned that when I focused on changing my process, the goal came much easier. I believe that Dr. Deming is saying the same thing. That it is actually influencing the processes within a system that will have the most effect on the results. At Tekmos we understand what Dr. Deming was saying. That it doesn't matter if you are discussing Quality, Production, or Engineering. It is the process and the system focus that will lead to the goals that we want, for ourselves, our products, and for the needs of our customers. Dr. Deming also said, "It is not necessary to change. Survival is not mandatory." Yes, I believe that Dr. Deming could make a profound point with sense of humor. Much as my Paw Paw did that day many years ago. For more information on Tekmos Quality Control... |

||

| Product Feature Corner | ||

|

Product Feature: TK68HC705C9A Microcontroller Tekmos' expanded line of microcontrollers includes the replacements for the NXP (Freescale) MC68HC705C8A and MC68HC705C9A microcontrollers. The TK68HC705C9A is an 8-bit microcontroller. The Tekmos TK68HC705C9A also has a configuration register that allows the part to be re-configured to replace both the MC68HC705C8A and the MC68HC705C12A. An interesting feature of the configuration register is that it changes the physical pinout of the TK68HC705C9A to match the pinout of the MC68HC705C8A. The TK68HC705C9A uses Flash to replace the original EPROM program storage. This means that while the original parts were OTP (One Time Programmable), the Tekmos version is fully re-programmable. The TK68HC05C9A is a ROM version of the part that provides a low cost solution for high volume production. Both the TK68HC705C8A and TK68HC705C9A are available in the 44-pin PLCC (FN), 40-pin PDIP (P) and space saving 44-pin PQFP (FB) packages. Contact us today at Sales for more information. |

||

| Blast From the Past: Tekmos Talks from March 2012 | ||

|

New Product Breakthrough: High Temperature ASIC's A worldwide shale gas and oil revolution has given Tekmos the opportunity to demonstrate its innovative High Temperature ASICs 225ºC and 125ºC to meet the oil and gas markets needs for drilling. Oil wells are measured downhole for a variety of parameters important for oil production. Temperature, pressure, and nuclear logging techniques where things like hydrocarbon % in the rock, porosity, lithology (composition of the rock) and water salinity all incorporate devices using high temperature ASIC's. As we all continue to work toward improved forms of clean energy Tekmos high temperature ASIC's will be useful in that pursuit including drilling for geothermal energy. Learn about Sandia National Laboratories' work about the technical challenges of high temperature well logging and the benefits of geothermal energy and drilling. For information about our high temperature chips contact Sales. |

||

| Thank You for Reading Tekmos Talks | ||

|

Thank you for reading Tekmos Talks and helping us celebrate 20 plus years. Sincerely, Lynn Reed, President

|

||

|

|

||

| A Newsletter for the Semiconductor Industry | ||

| March 2017 | ||

|

Welcome to Tekmos Talks March 2017. This month we will discuss Altera FPGA conversions, Part V of Dual Port Ram-Memory, launch a new product, and share Inside Tekmos' Cookout. |

||

| From the Desk of the President, Lynn Reed | ||

|

Altera FPGA Conversions Altera announced the discontinuation of many of their FPGA lines last December. This includes the MAX, Flex, and early Acex and Apex families. Customers are given the opportunity to make a last time buy of these products. And for many customers, this is the best choice. But for some customers, it is not the best choice. Making a last time buy means that you have a reasonable understanding of your future requirements, and you are willing to tie up capital to buy a multi-year supply of these products. If your products are continuing to do well, or even growing in volume, then it is both difficult and risky to forecast the entire future demand, and an FPGA conversion should be considered. The FPGA conversion will generally cost a lot less than the original FPGAs. But conversions also have an associated NRE. This produces a breakeven volume point where the unit savings equal the NRE charges. If this point is reached in 6 to 9 months, a conversion is economical. If it takes longer, then the conversion must be justified by other means, such as strategic availability. Tekmos has developed several methods of reducing the NREs, making it possible to lower the breakeven point. The first is what we call a merge. In a merge, we combine multiple designs on a single piece of silicon. Each individual design is activated through a bond option during assembly. This allows all the designs to share the costs of a mask set and a wafer run, which are the main components to a NRE charge. Of course, each design must be individually converted, assembled, and tested. Still, the NRE charge per part is much less than the charges if each part was individually converted. Merges have another advantage. By combining multiple designs on a single die, the volume for that die is the combined total for all the devices in the merge. Wafer fabs will make quarter half lots, but there is a financial penalty in doing so. A merge may allow a single order for multiple parts to obtain better wafer pricing. Another way to reduce costs is to use a more advanced technology for the FPGA conversion. For 180nm and up, all the NRE charges are equivalent. In many cases, the operating voltage will determine the technology. As a very rough rule of thumb, the technology * 10 is equal to the maximum operating voltage. This sets the minimum die size, and that sets the manufacturing costs. Tekmos can get around this limitation by using an on-chip voltage regulator to produce the lower core voltages while allowing the I/O voltages to be the same as the original FPGA. Since the newer technologies have significant density advantages, this can result in a smaller die size, and thus a lower cost. So, if you get an EOL notice from your FPGA vendor, remember that you do have options, and that Tekmos can help you realize those options. Contact us today at Sales for more information. Or fill out the FPGA questionnaire form here. Or to Request a Quote. |

||

| Part V Design of Dual Port RAM, by Lynn Reed | ||

|

Ram Timing In this final article about RAM design, I am going to discuss the timing necessary to make the RAM work. Between memory cycles, the RAM is in a precharge mode. All bit lines are being held at Vdd. All word lines are off. And the data latches are holding the last value that was read or written. The cycle begins when a chip enable signal is clocked into a flop. In a synchronous RAM, the clock is the RAM clock. In an asynchronous RAM, the clock is derived from a change in address lines. The rest of the RAM timing is asynchronously derived from the output of this flop. This means that the end of one step triggers the next step. Here is the sequence of RAM timing: