-

This email address is being protected from spambots. You need JavaScript enabled to view it.

Tekmos' Blog

Tekmos' Blog

Gate Array Architectures

Our 180 nm basic process has 24 mask layers. By using a gate array architecture for the digital logic and analog circuitry, it is possible to program a gate array with 3 to 4 metal layers, or 6 to 8 masks, counting the vias. Using an existing gate array reduces the mask cost by 66% to 75%. This puts the cost of the programming layers for a gate array on par with the costs for a shuttle run.

Another way of looking at this is to note that the costs of a shuttle run followed by a full mask set is comparable to the costs of a full mask set, followed by a programming layer revision, if necessary. And this approach can be much faster than a shuttle run. A shuttle run can take four months, while a gate array can be started before the final design is done, allowing wafers to be held at the first programming layer. So a gate array cycle can be 3 to 4 weeks, instead of 4 months.

In many cases, Tekmos may already have base wafers. For example, we have a base array with multiple block RAMs, clock modules, 256 pins, and a SERDES. If the customer design fits in this base, then the programming layers are the only masks that have to be purchased, resulting in a substantially lower NRE.

Design Merges

An approach for a customer with multiple designs is to merge the designs into a single circuit, and implement that as an ASIC. Each design can be activated as a bond option during assembly, and operate as a stand-alone chip. This approach shares the mask costs over several design, without the production die cost penalties associated with a shuttle run.

Design merges are complicated. When they share pins, you have to address potential conflicts between output strengths and input levels. Supply pins add a further complication. And it is essential that the circuit that is disabled not draw power when the other design is enabled. We joke that every semiconductor company has tried design merges, and every one of them has sworn to never do it again. But in our case, we have solved the problems, and regularly use design merges.

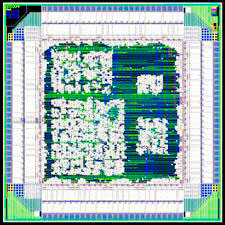

This drawing shows a merge of 4 designs on a single die.

Summary

Masks are expensive. But there are creative design and layout approaches that can substantially reduce them. Talk with us to find out how Tekmos can reduce your NRE costs.

When you subscribe to the blog, we will send you an e-mail when there are new updates on the site so you wouldn't miss them.